- 您现在的位置:买卖IC网 > Sheet目录329 > IDT7140LA55C (IDT, Integrated Device Technology Inc)IC SRAM 8KBIT 55NS 48DIP

�� �

�

�

�IDT7130SA/LA� and� IDT7140SA/LA�

�High-Speed� 1K� x� 8� Dual-Port� Static� SRAM�

�Military,� Industrial� and� Commercial� Temperature� Ranges�

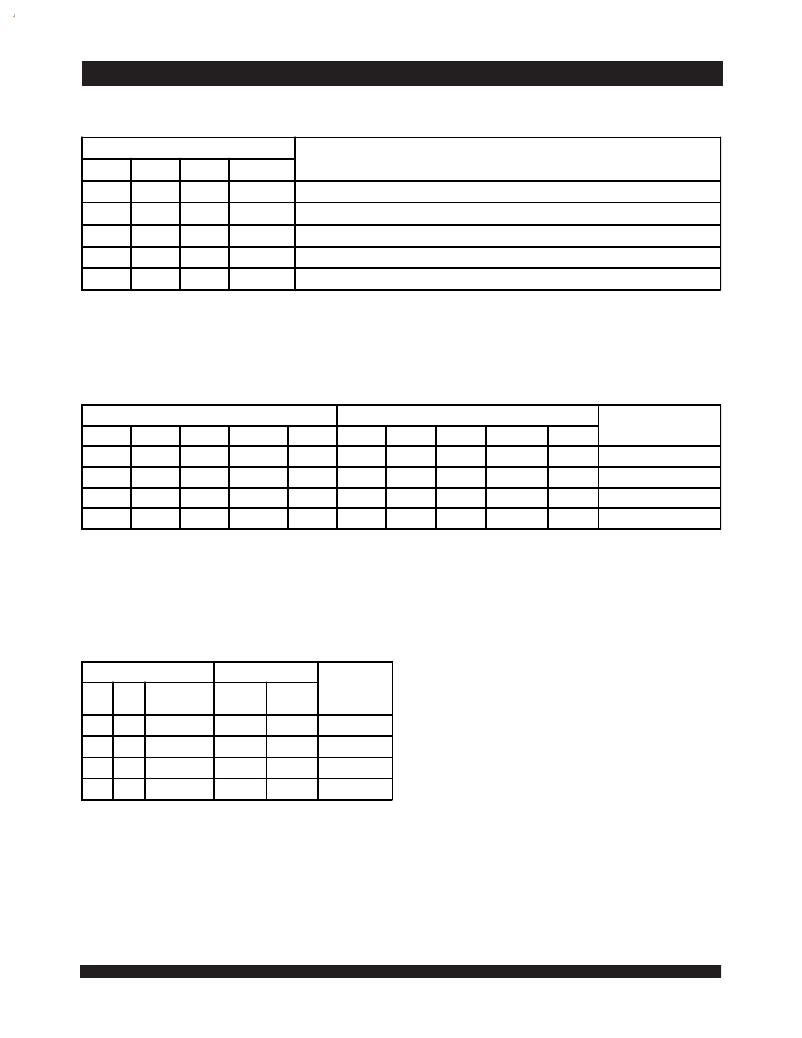

�Truth� Tables�

�Truth� Table� I� —� Non-Contention� Read/Write� Control� (4)�

�Inputs� (1)�

�R/� W�

�X�

�X�

�L�

�H�

�H�

�CE�

�H�

�H�

�L�

�L�

�L�

�OE�

�X�

�X�

�X�

�L�

�H�

�D� 0-7�

�Z�

�Z�

�DATA� IN�

�DATA� OUT�

�Z�

�Function�

�Port� Disabled� and� in� Power-Down� Mode,� I� SB2� or� I� SB4�

�CE� R� =� CE� L� =� V� IH� ,� Power-Down� Mode,� I� SB1� or� I� SB3�

�Data� on� Port� Written� into� Memory� (2)�

�Data� in� Memory� Output� on� Port� (3)�

�High� Impedance� Outputs�

�NOTES:�

�1.� A� 0L� –� A� 10L� ≠� A� 0R� –� A� 10R� .�

�2.� If� BUSY� =� L,� data� is� not� written.�

�3.� If� BUSY� =� L,� data� may� not� be� valid,� see� t� WDD� and� t� DDD� timing.�

�4.� 'H'� =� V� IH� ,� 'L'� =� V� IL� ,� 'X'� =� DON’T� CARE,� 'Z'� =� HIGH� IMPEDANCE�

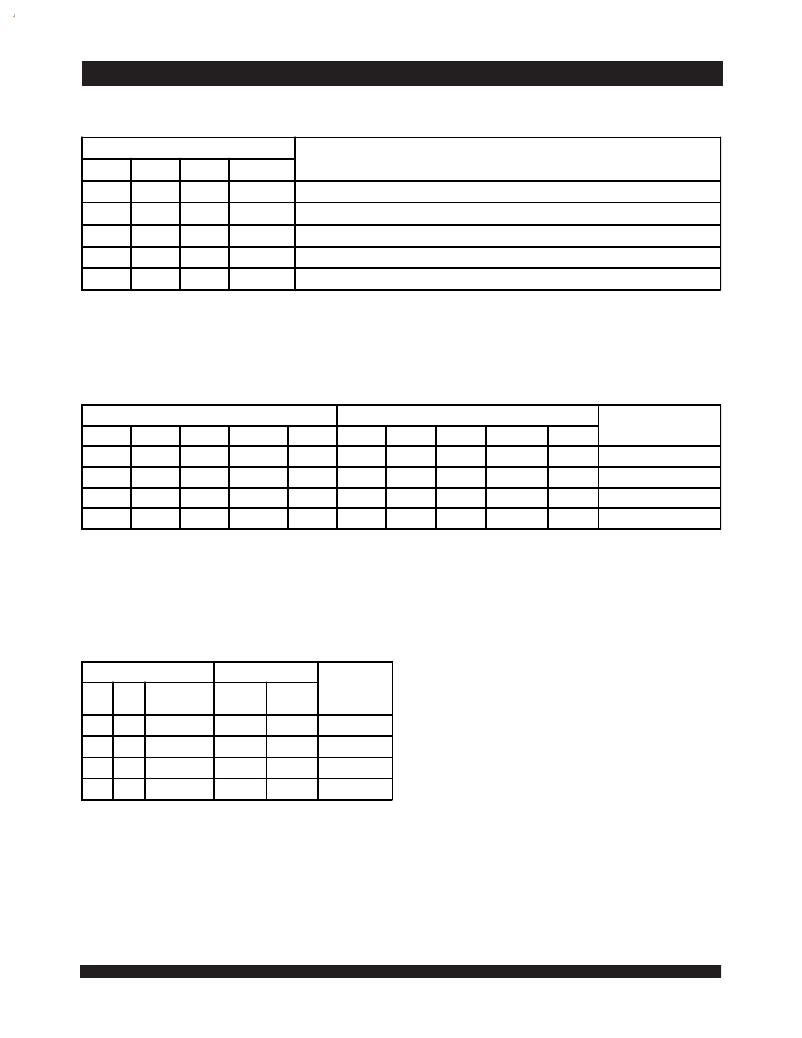

�Truth� Table� II� —� Interrupt� Flag� (1,4)�

�Left� Port�

�Right� Port�

�2689� tbl� 13�

�H�

�R/� W� L�

�L�

�X�

�X�

�X�

�CE� L�

�L�

�X�

�X�

�L�

�OE� L�

�X�

�X�

�X�

�L�

�A� 9L� -A� 0L�

�3FF�

�X�

�X�

�3FE�

�INT� L�

�X�

�X�

�L� (3)�

�(2)�

�R/� W� R�

�X�

�X�

�L�

�X�

�CE� R�

�X�

�L�

�L�

�X�

�OE� R�

�X�

�L�

�X�

�X�

�A� 9R� -A� 0R�

�X�

�3FF�

�3FE�

�X�

�INT� R�

�L� (2)�

�H� (3)�

�X�

�X�

�Function�

�Set� Right� INT� R� Flag�

�Reset� Right� INT� R� Flag�

�Set� Left� INT� L� Flag�

�Reset� Left� INT� L� Flag�

�NOTES� :�

�1.� Assumes� BUSY� L� =� BUSY� R� =� V� IH�

�2.� If� BUSY� L� =� V� IL� ,� then� No� Change.�

�3.� If� BUSY� R� =� V� IL� ,� then� No� Change.�

�4.� 'H'� =� HIGH,'� L'� =� LOW,'� X'� =� DON’T� CARE�

�Truth� Table� III� —� Address� BUSY�

�Arbitration�

�2689� tbl� 14�

�Inputs�

�Outputs�

�CE� L�

�X�

�H�

�X�

�L�

�CE� R�

�X�

�X�

�H�

�L�

�A� 0L� -A� 9L�

�A� 0R� -A� 9R�

�NO� MATCH�

�MATCH�

�MATCH�

�MATCH�

�BUSY� L� (1)�

�H�

�H�

�H�

�(2)�

�BUSY� R� (1)�

�H�

�H�

�H�

�(2)�

�Function�

�Normal�

�Normal�

�Normal�

�Write� Inhibit� (3)�

�NOTES:�

�2689� tbl� 15�

�1.� Pins� BUSY� L� and� BUSY� R� are� both� outputs� for� IDT7130� (master).� Both� are� inputs� for�

�IDT7140� (slave).� BUSY� X� outputs� on� the� IDT7130� are� open� drain,� not� push-pull�

�outputs.� On� slaves� the� BUSY� X� input� internally� inhibits� writes.�

�2.� 'L'� if� the� inputs� to� the� opposite� port� were� stable� prior� to� the� address� and� enable� inputs�

�of� this� port.� 'H'� if� the� inputs� to� the� opposite� port� became� stable� after� the� address� and�

�enable� inputs� of� this� port.� If� t� APS� is� not� met,� either� BUSY� L� or� BUSY� R� =� LOW� will�

�result.� BUSY� L� and� BUSY� R� outputs� can� not� be� LOW� simultaneously.�

�3.� Writes� to� the� left� port� are� internally� ignored� when� BUSY� L� outputs� are� driving� LOW�

�regardless� of� actual� logic� level� on� the� pin.� Writes� to� the� right� port� are� internally�

�ignored� when� BUSY� R� outputs� are� driving� LOW� regardless� of� actual� logic� level� on�

�the� pin.�

�18�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IDT7142LA55C

IC SRAM 16KBIT 55NS 48DIP

IDT7143LA25G

IC SRAM 32KBIT 25NS 68PGA

IDT7164L25YGI

IC SRAM 64KBIT 25NS 28SOJ

IDT71T75802S200PFGI

IC SRAM 18MBIT 200MHZ 100TQFP

IDT71T75902S85BGG

IC SRAM 18MBIT 85NS 119BGA

IDT71V016SA12PHGI

IC SRAM 1MBIT 12NS 44TSOP

IDT71V124SA10PHGI

IC SRAM 1MBIT 10NS 32TSOP

IDT71V256SA20PZG

IC SRAM 256KBIT 20NS 28TSOP

相关代理商/技术参数

IDT7140LA55CB

制造商:Integrated Device Technology Inc 功能描述:IC SRAM 8KBIT 55NS SB48

IDT7140LA55J

功能描述:IC SRAM 8KBIT 55NS 52PLCC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:2,000 系列:MoBL® 格式 - 存储器:RAM 存储器类型:SRAM - 异步 存储容量:16M(2M x 8,1M x 16) 速度:45ns 接口:并联 电源电压:2.2 V ~ 3.6 V 工作温度:-40°C ~ 85°C 封装/外壳:48-VFBGA 供应商设备封装:48-VFBGA(6x8) 包装:带卷 (TR)

IDT7140LA55J8

功能描述:IC SRAM 8KBIT 55NS 52PLCC RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:2,000 系列:MoBL® 格式 - 存储器:RAM 存储器类型:SRAM - 异步 存储容量:16M(2M x 8,1M x 16) 速度:45ns 接口:并联 电源电压:2.2 V ~ 3.6 V 工作温度:-40°C ~ 85°C 封装/外壳:48-VFBGA 供应商设备封装:48-VFBGA(6x8) 包装:带卷 (TR)

IDT7140LA55L48B

制造商:Integrated Device Technology Inc 功能描述:IC SRAM 8KBIT 55NS 48LCC

IDT7140LA55P

功能描述:IC SRAM 8KBIT 55NS 48DIP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:2,000 系列:MoBL® 格式 - 存储器:RAM 存储器类型:SRAM - 异步 存储容量:16M(2M x 8,1M x 16) 速度:45ns 接口:并联 电源电压:2.2 V ~ 3.6 V 工作温度:-40°C ~ 85°C 封装/外壳:48-VFBGA 供应商设备封装:48-VFBGA(6x8) 包装:带卷 (TR)

IDT7140LA55PF

功能描述:IC SRAM 8KBIT 55NS 64TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:2,000 系列:MoBL® 格式 - 存储器:RAM 存储器类型:SRAM - 异步 存储容量:16M(2M x 8,1M x 16) 速度:45ns 接口:并联 电源电压:2.2 V ~ 3.6 V 工作温度:-40°C ~ 85°C 封装/外壳:48-VFBGA 供应商设备封装:48-VFBGA(6x8) 包装:带卷 (TR)

IDT7140LA55PF8

功能描述:IC SRAM 8KBIT 55NS 64TQFP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:2,000 系列:MoBL® 格式 - 存储器:RAM 存储器类型:SRAM - 异步 存储容量:16M(2M x 8,1M x 16) 速度:45ns 接口:并联 电源电压:2.2 V ~ 3.6 V 工作温度:-40°C ~ 85°C 封装/外壳:48-VFBGA 供应商设备封装:48-VFBGA(6x8) 包装:带卷 (TR)

IDT7140SA100C

功能描述:IC SRAM 8KBIT 100NS 48DIP RoHS:否 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1,000 系列:- 格式 - 存储器:RAM 存储器类型:SRAM - 双端口,同步 存储容量:1.125M(32K x 36) 速度:5ns 接口:并联 电源电压:3.15 V ~ 3.45 V 工作温度:-40°C ~ 85°C 封装/外壳:256-LBGA 供应商设备封装:256-CABGA(17x17) 包装:带卷 (TR) 其它名称:70V3579S5BCI8